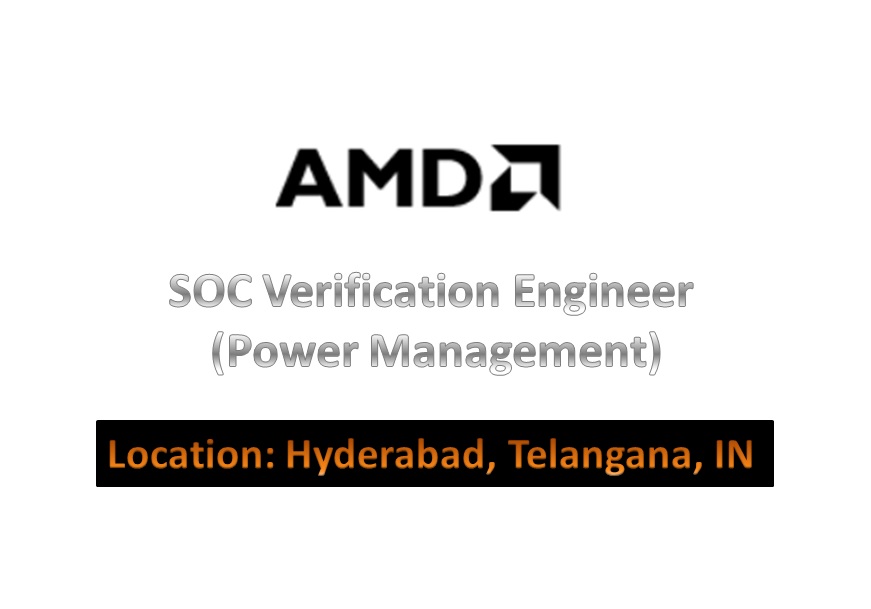

Introduction to UVM (Universal Verification Methodology)

The Universal Verification Methodology (UVM) is a standardized framework for building reusable and scalable testbenches to verify complex digital designs. It builds upon the capabilities of SystemVerilog, providing a structured and efficient approach to functional verification. UVM has become the industry standard for verifying large-scale designs, from SoCs to complex subsystems, ensuring that they meet functional requirements before fabrication.

Real-Life Analogy: UVM vs. SystemVerilog

Imagine you’re managing the construction of a skyscraper.

- SystemVerilog: Think of SystemVerilog as the tools used in construction—hammers, drills, and saws. These tools are essential, but their usage depends on the skill and creativity of the worker.

- UVM: Now imagine you have a construction blueprint and a workflow system that organizes the tools, materials, and teams in a systematic way. UVM provides this framework, ensuring that everything works cohesively, saving time and resources while guaranteeing quality.

In essence, UVM is built on top of SystemVerilog, combining its raw power with structure and methodology, much like how a construction management system enhances the efficiency of individual tools.

How UVM Differs from SystemVerilog

| Aspect | SystemVerilog | UVM |

|---|---|---|

| Purpose | Language for modeling and verification. | Framework for creating reusable, modular testbenches. |

| Focus | Writing code for simulation and testing. | Managing testbench architecture and processes. |

| Reuse | Limited out-of-the-box reuse capabilities. | Built-in reuse mechanisms (agents, sequences, etc.). |

| Standardization | Syntax and constructs can vary across projects. | Provides standardized components and workflows. |

| Advanced Features | Requires custom implementation for many features. | Offers built-in TLM, coverage, and reporting features. |

| Learning Curve | Easier to start but can get unstructured for large projects. | Steeper learning curve but highly efficient for complex designs. |

Key Contents of UVM

- UVM Components

UVM provides a modular structure where each component has a specific role:- UVM Test: Controls the overall test execution.

- UVM Environment: Encapsulates all components required for verification.

- UVM Agent: Includes drivers, monitors, and sequencers for specific interfaces.

- UVM Driver: Sends stimulus to the DUT (Design Under Test).

- UVM Monitor: Observes DUT outputs and sends data to the scoreboard.

- UVM Scoreboard: Compares expected and actual results to identify mismatches.

Analogy:

Think of these components as parts of a car’s testing assembly line:

- Driver acts as the conveyor belt feeding materials (stimulus).

- Monitor inspects every assembled part.

- Scoreboard is the quality control team ensuring the car meets specifications.

- Transaction-Level Modeling (TLM)

- Enables efficient communication between UVM components.

- Allows passing abstract data structures (transactions) instead of low-level signals.

Analogy:

Rather than manually handling nuts and bolts, TLM lets you focus on assembling entire parts, saving time and effort.

- Sequences and Sequencers

- Sequences: Define various test scenarios by generating specific stimulus patterns.

- Sequencers: Coordinate the execution of sequences.

Analogy:

Think of sequences as different recipes and the sequencer as the chef managing which recipe to prepare and when.

- UVM Factory

- Enables dynamic creation and configuration of components.

- Promotes flexibility and reuse by allowing runtime changes.

Analogy:

Imagine a factory that can switch between producing cars, bikes, or trucks based on demand. Similarly, the UVM Factory adapts your testbench as per the verification needs.

- UVM Reporting

- Provides standardized methods for logging messages, warnings, and errors.

- Helps in debugging by categorizing issues.

Analogy:

This is like a dashboard in your car, showing real-time alerts and information to the driver, ensuring smooth operations.

- Functional Coverage

- Tracks which scenarios or conditions have been tested.

- Helps in identifying gaps in verification.

Analogy:

Think of it as a checklist for a road trip, ensuring you’ve visited all planned destinations.

- UVM Phases

- Provides a standardized sequence for testbench execution (e.g.,

build_phase,run_phase,check_phase). - Ensures orderly initialization, execution, and cleanup.

- Provides a standardized sequence for testbench execution (e.g.,

Analogy:

It’s like a detailed event plan for a wedding, ensuring all ceremonies happen in the right sequence.

Benefits of UVM

- Reusability: Write once, reuse across projects.

- Modularity: Break down testbenches into manageable components.

- Scalability: Efficiently handle complex designs with millions of gates.

- Debugging Efficiency: Structured reporting and monitoring reduce debugging time.

Conclusion

UVM transforms the verification process, much like how automation revolutionizes production lines. It standardizes workflows, enhances productivity, and ensures the robustness of digital designs. While SystemVerilog provides the tools, UVM offers the methodology to use them effectively.

By mastering UVM, you not only improve your verification capabilities but also position yourself as a key player in the semiconductor industry. Dive into UVM today and gear up for a successful career in design verification!